ディップメータ2

2011年9月に購入した中国製オシロスコープにより6月に製作したディップメータの波形を観測したところ、あまりにも汚い波形であることに仰天しました。

恥かしながら汚い波形の例をいくつかお見せしたうえで、どのようにしてこれを改善して行ったかをご紹介します。

改善前の波形

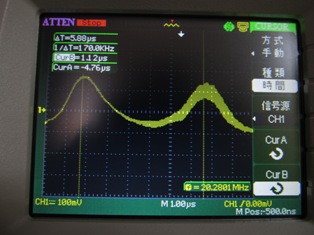

波形1とします。

所々にこのような特異点がありました。

周波数記録なし。

この波形ではオシロのカウンタは当てになりません。

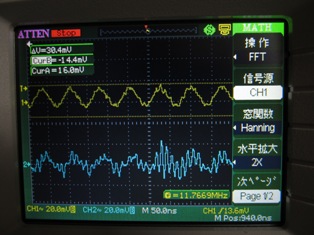

波形2とします。

これは11MHz辺り。(周波数記録あり)

上段がFETバッファ1段目のゲート、下段がソース。

波形3とします。

これは45MHz辺り。(周波数記録あり)

上段、下段は同上。

原因

主な要因は、デジタル系(周波数カウンタ)からアナログ系(ディップメータ回路)へのノイズの混入です。

切り分け

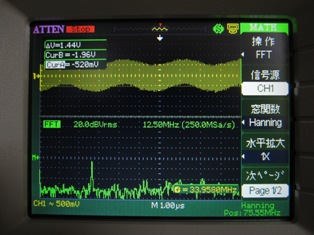

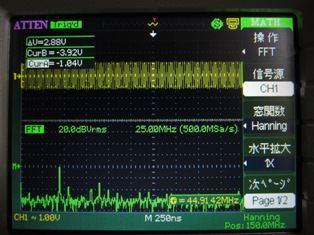

波形4とします。

33MHz辺りの波形ですが、全体に低周波(160KHzくらい)のノイズが重畳してうねった波形になっています。

下段は周波数スペクトラムですが、左端にあるのがノイズのスペクトラムです。

デジタル周波数カウンタの電源をオフにするとうねりがなくなるので、重畳していたノイズはカウンタのものとわかります。

左端のスペクトラムは消滅しています。

またこの波形以外でも、カウンタをオフにすると全体に波形は改善する方向にあります。

対策

対策1

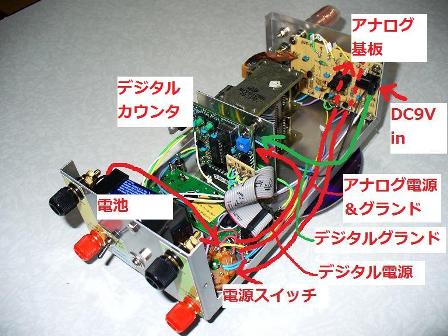

カウンタからの放射ノイズを防止するためにシールドボックスを作りました。全体のレイアウトは変えずに無理やり壁を立てた感じです。

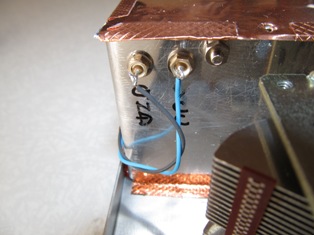

カウンタ電源ラインからの伝導ノイズを低減するために電源、グランド線の引き出しには貫通コンデンサを使用しました。シールドボックスの右下に2つ見えている白いものがそうです。

同じく伝導ノイズ低減のためEMI対策用コアをシールドボックス内部で電源、グランド線に巻いていますが気休め程度です。

貫通コンデンサ取り付けの様子。

貫通コンデンサは秋葉原の東京ラジオデパート2階、山王電子で購入。

品揃えがよいうえ店主の方がとても感じがよいのでコンデンサ関係はたいていここで買っています。

シールドした結果、波形はきれいに平らになりました(少し見ている周波数がずれていますが、33MHzでも同様です)。カウンタの電源はオンのため、

左端のスペクトラムは少し見えています。

しかし、波形2、3、および全体にぼーっとノイズぽいものが残っています。

対策2

電源、グランドラインの引き回し

波形2,3についても、カウンタをオフにすると改善されることから、対策1のシールドボックスにより放射ノイズの影響は著しく低減されたものの、電源、グランドラインからのデジタルノイズの漏れ出しは貫通コンデンサでは取りきれないものと考え、電源、グランドラインの引き回しを変更しました。

グランド方法

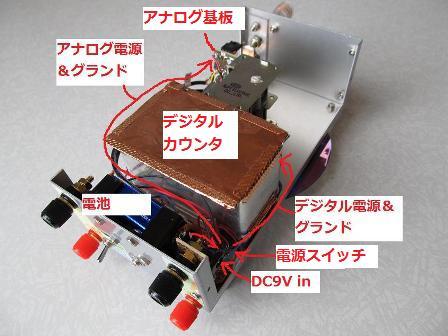

これまでは高周波回路ということでその場その場で最短でシャーシに落とす考えでしたが、これではアナログ回路とデジタル回路が共通インピーダンスを持ってしまいアナログ波形に悪影響を及ぼすと考え、アナログ系とデジタル系のグランドを分離し、バリコンのシャーシへの取り付けネジへの1点でグランド(FG)を取ることに変更しました。

アナログ回路のノイズ感度

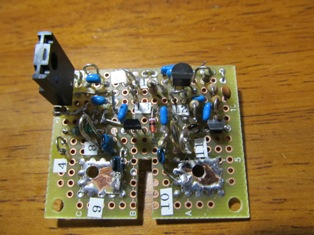

アナログ回路が極力デジタルノイズを受けないようにするため、回路基板を小さく作り直し、バリコンの端子に直接固定しました。

以前は下の写真のように、DC9V inのジャックが向こう側のアナログ基板上に、電池が手前側にあったため、これらの線を手前の電源スイッチを経由してアナログ基板とデジタルカウンタに向かわせるために線が錯綜していました。この結果、デジタルカウンタからデジタル電源&グランドラインに漏れ出たデジタルノイズがアナログ電源&グランドに誘導しやすいレイアウトになっていました。

これを改善するため、下の写真のようにDC9V inジャックを手前側に配置換えし、行ったり来たりのないすっきりした配線を実現しました。

これによって、デジタルノイズがアナログ系に誘導しにくくなりました。

なお、シールドボックスの固定は数箇所のネジ止めだけでは心もとないのでスコッチの銅テープで四周を目張りしました。

アナログ基板はこのようにガラエポ基板にコンパクトにまとめ、バリコンの端子に直接M2のビス、ナットで取り付けました。

M2のナットがラジペンではうまく締まらず、ホームセンターに小型ナットまわしを買いに走りました。

ナット締めするところには銅箔を長方形に切ったものをランドとして貼り付けて(半田付けして)あります。

この写真ではエミッタフォロワ用のトランジスタ(2SC1815)が写っていますが、その後使わなくなったので電源供給を切り離し、信号はパスさせています。

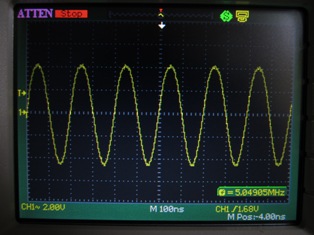

改善後の波形

以上の対策の結果、奇怪な波形を追放することができ、基本的にすっきりした正弦波の波形になりました。

5MHz近辺での波形です。

何の変哲もない正弦波ですが、ここまで来るのはなかなか大変でした。

VHF領域では、振幅の揺らぎが少し出てきます。

5MHz近辺での波形をFFTで見たところです。

上段の時間軸波形は遅くして見てもきれいです。

・・・・オシロの画面が解像度が低い(320×234画素)LCDのため、干渉縞のようなものが見えています

スペクトラムは、5MHzの基本波だけというわけには行かず、高調波がばっちり見えています。

回路変更

回路図は実装状態の変更に対応して以下のとおり修正しました。

また、発振信号取り出し用のバッファはこれまでFETのソースフォロワ1段通したものをカウンタへ、さらにもう一段通したものを外部出力へ供給していたのですが、評価の結果、一段だけでカウンタと外部出力の双方に供給することにしました。

ここは、FETソース接地増幅回路、ソースフォロワ回路、トランジスタによるエミッタフォロワ回路を試したのですが、以下のような周波数特性であることがわかりました。FETは2SK241-GR、トランジスタは2SC1815-GRを使用。

ソース接地増幅回路:

→周波数が高くなるほどゲインが直線的に落ちてき、20MHz以上ではゲインが1以下になる。

ソースフォロワ回路:

→70MHzあたりまでほぼフラット(微減)。

エミッタフォロワ回路:

→70MHzあたりまでフラット。

入出力の周波数特性としてはエミッタフォロワが一番よかったのですが、

72MHzあたりでのみ波形が段付きになりカウンタが正確に表示できない問題があるため、エミッタフォロワよりもフラットさが劣るものの全域で波形の乱れがなかったソースフォロワ回路を採用しました。

回路定数など、前のものから一部変更しています。

当初の考えでは、1段目の出力をカウンタと外部出力の両方に供給すると外部出力側に接続した負荷によりカウンタの表示に影響を及ぼすことを避けるために2段目バッファをつけたのですが、70MHz以上で減衰のある回路を2段重ねると70MHz以上の減衰が激しくなるため2段目はやめにしました。その代わり外部出力に50Ωの負荷をつなげてもカウンタの表示に影響はないことを確認しました。

なお、測定は100MHz帯域の中国製オシロスコープで行いましたが、70MHz以上の測定についても入出力の相対比較なので、オシロの帯域の影響はないものと考えています。

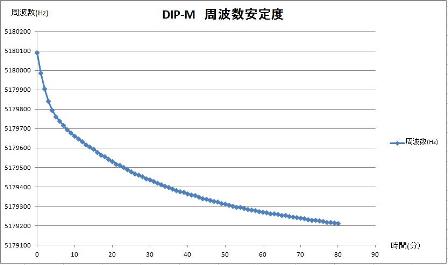

周波数安定度

波形改善の目的は達成したので、内蔵のカウンタで周波数安定度を測定してみました。

周波数は5MHz近辺。

測定時の室温は15.5度程度、測定時間中の温度変化は0.5度以内です。

80分測定し、約900Hz程度下がってもうすぐサチるかな、というところです。

ディップメータとしては、この程度の安定度があれば問題はないでしょう。

ひとこと

40年振りのアマチュア無線復帰の皮切りに製作したディップメータでしたが考えが甘かったようです。安易にデジタル周波数カウンタを内蔵したのが苦労のもと。

やはりデジアナ混在回路は心して作ろうということです。

(2011/12/11)

感想などありましたらこちらへお願いします。→ここをクリック

a:8139 t:3 y:2